# **COURSE DESCRIPTOR BOOKLET**

## **M.Tech(Embedded Systems)**

## **ELECTRONICS AND COMMUNICATION ENGINEERING**

(Accredited by NBA)

## **R-18 REGULATIONS**

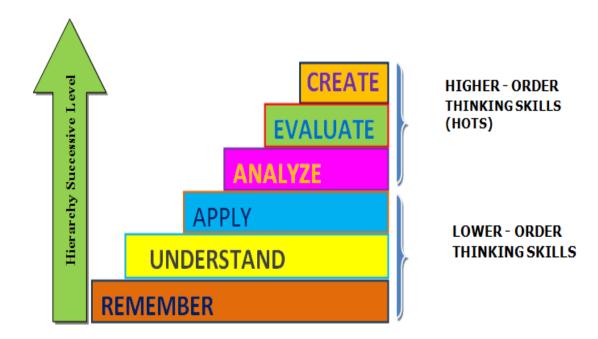

## **BLOOM'S TAXONOMY OF LEARNING OUTCOMES**

.....Moving Towards Perfection in Engineering

## **INSTITUTE OF AERONAUTICAL ENGINEERING**

(Autonomous)

Approved by AICTE; Affiliated to JNTUH and Accredited by NAAC with 'A' Grade Dundigal, Hyderabad - 500 043

### Vision

To produce professionally competent Electronics and Communication Engineers capable of effectively and efficiently addressing the technical challenges with social responsibility.

### Mission

The mission of the Department is to provide an academic environment that will ensure high quality education, training and research by keeping the students abreast of latest developments in the field of Electronics and Communication Engineering aimed at promoting employability, leadership qualities with humanity, ethics, research aptitude and team spirit.

| S. No. |                                                                                 | Page No. |  |  |  |  |  |

|--------|---------------------------------------------------------------------------------|----------|--|--|--|--|--|

|        | PART – I                                                                        |          |  |  |  |  |  |

|        | (As Per NBA Norms post June, 2015)                                              | 5        |  |  |  |  |  |

| 1      | 1 Program Educational Objectives, Outcomes and Assessment Criteria              |          |  |  |  |  |  |

| 2      | M. Tech – Embedded systems Program Educational Objectives                       | 6        |  |  |  |  |  |

| 3      | M. Tech - Embedded systems Program Outcomes                                     | 8        |  |  |  |  |  |

| 4      | Mapping of Program Educational Objectives to Program Outcomes                   | 9        |  |  |  |  |  |

| 5      | Relation between the Program Outcomes and the Program Educational Objectives    | 10       |  |  |  |  |  |

| 6      | Program Outcomes of M.Tech, Embedded systems Masters.                           | 11       |  |  |  |  |  |

| 7      | Procedures for Outcome Delivery and Assessment with Respect to Program Outcomes | 13       |  |  |  |  |  |

| 8      | Methods of Measuring Learning Outcomes and Value Addition                       | 15       |  |  |  |  |  |

| A.     | PART – II<br>SSESSMENT OF COURSE LEVEL STUDENT LEARNING OUTCO                   | OMES     |  |  |  |  |  |

| 1      | Course Purpose                                                                  | 20       |  |  |  |  |  |

| 2      | Expected Learning Outcomes                                                      | 21       |  |  |  |  |  |

| 3      | To Define Effective Learning Outcome Statements                                 | 21       |  |  |  |  |  |

| 4      | Tips for Developing Course Level Expected Learning Outcomes Statements          | 23       |  |  |  |  |  |

| 5      | Sample Expected Learning Outcomes Statements                                    | 23       |  |  |  |  |  |

| 6      | An Overview of Assessment                                                       | 24       |  |  |  |  |  |

| 7      | Description of a Course Purpose                                                 | 25       |  |  |  |  |  |

| 8      | Procedure for Development of Expected Learning Outcomes for a Course            | 26       |  |  |  |  |  |

| 9      | References                                                                      | 27       |  |  |  |  |  |

|        | ANNEXURES                                                                       |          |  |  |  |  |  |

| А      | Sample Course Description (As Per NBA Norms post June, 2015)                    | 28       |  |  |  |  |  |

Contents Program Education Objectives and Outcomes

As Per NBA Norms Post June, 2016 Semester: I-I, I-II, II-I, II-II

## Part – I

#### **PROGRAM EDUCATIONAL OBJECTIVES AND OUTCOMES**

First version 22 July, 2014

## **Program Educational Objectives, Program Outcomes and Assessment Criteria** (Approved by DAC ECE on 3/9/2014):

**Electronics and Communication Engineering Department Advisory Council:** The Electronics and Communication Engineering Department Advisory Council (ECEDAC) includes a diverse group of experts from academic and industry, as well as alumni representation. The Advisory Board meets annually, or as needed, for a comprehensive review of the Electronics and Communication Engineering Department strategic planning and programs. The Advisory Council meets with administration, faculty and students and prepares a report, which is presented to principal. In each visit, the Department of Electronics and Communication Engineering responds to the report indicating improvements and amendments to the program.

## 1. PROGRAM EDUCATIONAL OBJECTIVES, OUTCOMES AND ASSESSMENT CRITERIA

#### Learning Outcomes, Assessment Criteria

The educational aims of a module are statements of the broad intentions of the teaching team. They indicate the objectives that the teaching team intends to cover and the learning opportunities that are necessary to be available to the student. A learning outcome is a statement that indicates the content that a learner (student) is expected to know, understand and/or be able to do at the end of a period of learning. It is advisable to express learning outcomes with the common prefix:

'On completion of (the period of learning e.g. module), the student is expected to be able to...'

Generally, learning outcomes do not specify curriculum, but more general areas of learning. It is not possible to prescribe precisely how specific a learning outcome statement should be. There is a balance to be struck between the degree of specificity in a learning outcome statement and that achieved by the assessment criteria. If there are too many learning outcomes for a module, then either they are becoming assessment criteria or they are specifying too much curricular detail. The curriculum should be described in the range statement. Too few learning outcomes are unlikely to provide sufficient information on the course. As a guide, there should be between 4 and 8 learning outcomes for a course.

The Program Educational Objectives (PEOs) of the Electronics and Communication Engineering department are broad statements or road maps describing career and professional objectives that intend the graduates to achieve through this program.

#### 2. M. TECH – EMBEDDED SYSTEMS PROGRAM

#### **EDUCATIONAL OBJECTIVES**

A graduate of Institute of Aeronautical Engineering in Embedded systems discipline should have a successful career in Electronics and Communication Engineering or a related field, and within three to five years, should attain the following:

#### **PROGRAM EDUCATIONAL OBJECTIVES:**

#### **PEO1.** Research and development

Be successful practicing professionals or pursue doctoral studies in allied areas, contributing significantly to **research and development** activities

#### **PEO2.** Demonstrate

**Demonstrate** technical competence, such as identifying, formulating, analyzing, and creating engineering solutions using appropriate current embedded engineering techniques, skills, and tools.

#### **PEO3.** Communicate

To work and **communicate** effectively in inter-disciplinary environment, either in a team or independently and establish leadership qualities.

#### **PEO4.** Apply

An ability to **apply** in-depth knowledge to evaluate, analyze and synthesize existing and novel designs.

These objectives are quite broad by intention, as Electronics and Communication Engineering graduates may seek further education or work in diverse areas. To make these objectives meaningful, they may be demonstrated by performance, actions, or achievements.

## i. To prepare the students who will be able to attain a solid foundation in Embedded systems fundamentals with an attitude to pursue continuing education.

- □ Make the students to understand their aptitude to choose the correct path of study which leads to higher qualifications and heights in the chosen field.

- □ Should be prepared to undergo rigorous training in their fields of working.

- □ Be capable of utilizing the solid foundation obtained at institute to apply successfully in solving the real time engineering problems.

- □ Students need to have creative thinking processes that are acquired through good training to find solutions to engineering problems.

## ii. To prepare the students to function professionally in an increasingly international and rapidly changing world due to the advances in technologies and concepts and to contribute to the needs of the society.

- Adoptability and accommodative mind set to suit modern world and changing economies.

- □ By working hard in the chosen field and sharing the professional experience at different forums within and outside the country.

- Desirable to be a member of various professional societies (IEEE, IETE, ISTE, IE, and etc.) to keep yourself abreast with the state-of-the-art technology.

- □ Should continue additional education in a broad range of subjects other than engineering may be needed in order to meet professional challenges efficiently and effectively.

- Continuous interaction with educational and research institutions or industrial research labs.

- □ Have a sound foundation of knowledge within a chosen field and achieve good depth and experience of practice in it.

- □ Able to relate knowledge within chosen field to larger problems in society and able to appreciate the interaction between science, technology, and society.

- □ Strong grasp of quantitative reasoning and an ability to manage complexity and ambiguity.

- □ To conduct research, and design, develop, test and oversee the development of electronic systems for global upliftment.

- □ Applying scientific knowledge to solve technical problems and develop products and services that benefit the society.

- □ An electronic engineer shall contribute to the society by research, design and development, testing and evaluation, application by manufacturing, maintenance by service, management and other functions like sales, customer service and etc.

## iii. To prepare the students to acquire and exercise excellent leadership qualities, at various levels appropriate to their experience, to address issues in a responsive, ethical, and innovative manner.

- Gives ample opportunity to work in diverse fields to acquire leadership roles in professional circles outside the workplace.

- □ Should keep in mind that the opportunities may change with the times.

- □ Should be prepared for creative solo and collaborative brainstorming sessions.

- Be able to inspire the team with selfless motivation and attitude to achieve success.

- □ Ability to think laterally or at-least have a flexibility of thought and make choices based on the requirement for situation.

## iv. To prepare the students who will be able to excel, in their careers by being a part of success and growth of an organization, with which they are associated.

- □ To achieve this, the focus should not be limited to an engineering curriculum and even to the class room.

- □ Continuing professional education by attending short term in courses design to update engineering skills.

- □ A lifelong commitment to learning new and specialized information.

- □ Should accept first person responsibility and should take the initiative in carrying out the work.

- □ Should be determined for the duty and dedicated to work and have passion for that.

- □ Be delight at work with a positive attitude.

- □ Should be a detailed worker so that one can be relied by the organization.

The department of Electronics and Communication Engineering periodically reviews these objectives and as part of this review process, encourages comments from all interested parties including current students, alumni, prospective students, faculty those who hire or admit our graduates to other programs members of related professional organizations, and colleagues from other educational institutions.

#### 3. M. TECH – EMBEDDED SYSTEMS PROGRAM OUTCOMES:

Masters of the embedded systems Program Outcomes will demonstrate:

#### **PROGRAM OUTCOMES:**

#### **PO1.** Engineering Knowledge

Apply advanced level knowledge, techniques, skills and modern tools in the field of Embedded Systems and sub areas IoT, Processor technology, and Storage technology.

#### PO2. Teamwork and Project Management

Function on multidisciplinary environments by working cooperatively, creatively and responsibly as a member of a team.

#### **PO3.** Develop and Novel Designs

Respond to global policy initiatives and meet the emerging challenges with sustainable technological solutions in the field of electronic product designing.

#### PO4. Analyze Complex Systems

Demonstrate the importance of embedded technologies and design new innovative products for solving society relevant problems.

#### PO5. Technical Presentation Skills

Write and present a substantial technical report / document.

#### **PO6.** Development of Solutions

Independently carry out research / investigation and development work to solve practical problems.

#### **PO7.** Lifelong learning

Recognize the need to engage in lifelong learning through continuing education and research.

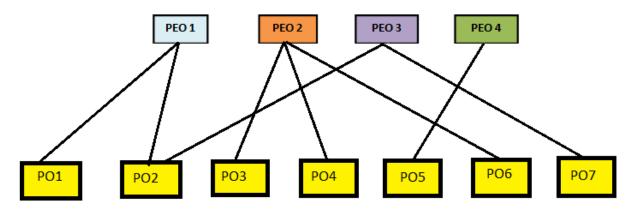

#### 4. MAPPING OF PROGRAM EDUCATIONAL OBJECTIVES TO PROGRAM OUTCOMES AND PROGRAM SPECIFIC OUTCOMES

The following Figure shows the correlation between the PEOs and the POs and PSOs

Figure: Correlation between the PEOs and the POs

| The following Table shows the correlation between the Program Education | nal Objectives and the |

|-------------------------------------------------------------------------|------------------------|

| Program Outcomes & Program Specific Outcomes                            |                        |

|     | Program Educational Objectives                                                                                                                                              |            | Program Outcomes                                                                                                                                                                                               |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T   |                                                                                                                                                                             | DO1        |                                                                                                                                                                                                                |

| I   | Be successful practicing professionals or<br>pursue doctoral studies in allied areas,<br>contributing significantly to <b>research and</b><br><b>development</b> activities | PO1        | <b>Engineering Knowledge</b><br>Apply advanced level knowledge, techniques, skills<br>and modern tools in the field of Embedded Systems<br>and sub areas IoT, Processor technology, and Storage<br>technology. |

|     |                                                                                                                                                                             | PO2        | <b>Teamwork and Project Management</b><br>Function on multidisciplinary environments by<br>working cooperatively, creatively and responsibly as<br>a member of a team.                                         |

| II  | To be in a position to analyze real life                                                                                                                                    | PO3        | Develop and Novel Designs                                                                                                                                                                                      |

|     | problems and design socially accepted and<br>economically feasible solutions in the<br>respective fields.                                                                   |            | Respond to global policy initiatives and meet the<br>emerging challenges with sustainable technological<br>solutions in the field of electronic product designing.                                             |

|     |                                                                                                                                                                             | PO4        | Analyze Complex Systems<br>Demonstrate the importance of embedded<br>technologies and design new innovative products<br>for solving society relevant problems.                                                 |

|     |                                                                                                                                                                             | PO6        | <b>Development of Solutions</b><br>Independently carry out research / investigation and development work to solve practical problems.                                                                          |

| III | To work and <b>communicate</b> effectively in                                                                                                                               | <b>PO2</b> | Teamwork and Project Management                                                                                                                                                                                |

|     | inter-disciplinary environment, either                                                                                                                                      |            | Function on multidisciplinary environments by                                                                                                                                                                  |

|     | independently or in a team, and establish                                                                                                                                   |            | working cooperatively, creatively and responsibly as                                                                                                                                                           |

|    | leadership qualities.                            |            | a member of a team.                                                                                                         |

|----|--------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------|

|    |                                                  | <b>PO7</b> | <b>Lifelong learning</b><br>Recognize the need to engage in lifelong learning<br>through continuing education and research. |

| IV | An ability to <b>apply</b> in-depth knowledge to | <b>PO5</b> | Technical Presentation Skills                                                                                               |

|    | evaluate, analyze and synthesize existing        |            | Write and present a substantial technical report /                                                                          |

|    | and novel designs.                               |            | document.                                                                                                                   |

#### 5. RELATION BETWEEN THE PROGRAM OUTCOMES AND PROGRAM EDUCATIONAL OBJECTIVES

A broad relation between the Program Educational Objectives and the Program Outcomes is given in the following table:

|     | PEOs                            | (1)             | (2)         | (3)         | (4)   |

|-----|---------------------------------|-----------------|-------------|-------------|-------|

| POs |                                 | Research<br>and | Demonstrate | Communicate | Apply |

|     |                                 | development     |             |             |       |

| PO1 | Engineering Knowledge           | 3               |             |             |       |

| PO2 | Teamwork and Project Management | 3               |             | 1           |       |

| PO3 | Develop and Novel Designs       |                 | 3           |             |       |

| PO4 | Analyze Complex Systems         |                 | 3           |             |       |

| PO5 | Technical Presentation Skills   |                 |             |             | 3     |

| PO6 | Development of Solutions        |                 | 3           |             |       |

| PO7 | Lifelong learning               |                 |             | 3           |       |

#### Relationship between Program Outcomes and Program Educational Objectives Key: 3 = Highly Related; 1 = Low

#### 6. PROGRAM OUTCOMES OF (M.Tech) EMBEDDED SYSTEMS MASTERS

Masters from accredited programs must achieve the following learning outcomes, defined by broad areas of learning.

The outcomes are distributed within and among the courses within our curriculum, and our students are assessed for the achievement of these outcomes, as well as specific course learning objectives, through testing, surveys, and other faculty assessment instruments. Information obtained in these assessments is used in a short-term feedback and improvement loop.

Each Electronics and Communication Engineering student will demonstrate the following attributes by the time they masters:

#### **PO1. Engineering Knowledge**

## Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems

Performance Criteria Definitions

- □ Identify the concepts and/or equations

- □ Execute the solution using a logic and structured approach

- **□** Evaluate the solution of the problem

#### **PO2. Teamwork and Project Management**

Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments

Performance Criteria Definitions

- □ Awareness of global effects of the product / practice / event

- □ Understanding of economic factors

- Awareness of implications to society at large

#### **PO3.** Develop Novel designs

Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations

Performance Criteria Definitions

- **u** Use modern engineering tools for the system design, simulation and analysis

- □ Use software applications effectively to write technical reports and oral presentations

- □ Use modern equipment and instrumentation in the design process, analysis and troubleshooting

#### **PO4.** Analyze Complex Systems

Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions

Performance Criteria Definitions

- □ Identify problem/purpose

- □ Prepare hypothesis

- □ Outline procedure

- □ List materials and equipment

- Conduct experiment

- □ Record observations, data and results

- □ Perform analysis

- Document conclusions

#### **PO5.** Technical Presentation skills

Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions *Performance Criteria Definitions*

- **u** Use appropriate format and grammatical structure

- Create a well organized document

- □ Present the results appropriately

- Demonstrate effective oral communication

#### **PO6.** Development of Solutions

Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations

Performance Criteria Definitions

- □ Awareness of global effects of the product / practice / event

- □ Understanding of economic factors

- Awareness of implications to society at large

#### **PO7.** Life-long Learning

Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change

Performance Criteria Definitions

- **□** Find relevant sources of information

- **D** Participate in school or professional seminars

- □ Participate in students or professional associations

I SEMESTER

**INSTITUTE OF AERONAUTICAL ENGINEERING**

(Autonomous) Dundigal, Hyderabad -500 043

#### **ELECTRONICS AND COMMUNICATION ENGINEERING**

#### **COURSE DESCRIPTOR**

| Course Title          | EMBEDDED                                                                      | EMBEDDED SYSTEM DESIGN          |  |   |          |  |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------|---------------------------------|--|---|----------|--|--|--|--|--|

| Course Code           | BESB01                                                                        | BESB01                          |  |   |          |  |  |  |  |  |

| Programme             | M.Tech                                                                        | M.Tech                          |  |   |          |  |  |  |  |  |

| Semester              | Ι                                                                             | Ι                               |  |   |          |  |  |  |  |  |

| Course Type           | Core                                                                          |                                 |  |   |          |  |  |  |  |  |

| Regulation            | IARE - R18                                                                    |                                 |  |   |          |  |  |  |  |  |

|                       |                                                                               | Theory                          |  | P | ractical |  |  |  |  |  |

| Course Structure      | Lectures         Tutorials         Credits         Laboratory         Credits |                                 |  |   |          |  |  |  |  |  |

|                       | 3 - 3                                                                         |                                 |  |   |          |  |  |  |  |  |

| <b>Course Faculty</b> | Mr. K.Ravi, A                                                                 | Mr. K.Ravi, Assistant Professor |  |   |          |  |  |  |  |  |

#### I. COURSE OVERVIEW:

Embedded systems have become the next inevitable wave of technology, finding application in diverse fields of engineering. The goal of this course is to impart training to graduate engineers, in specialized area of Embedded Systems so that they can develop expertise in developing and deploying embedded systems over a wide range of applications. This course provides the basic knowledge over the hardware units and devices for design of embedded systems. It also provides the information about the Use architectures of embedded RISC processors and system on chip processor design of embedded systems. This course is intended to Analyze interrupt latency, context switching time, for development of device drives for timing devices.

#### II. COURSE PRE-REQUISITES:

| Level | Course<br>Code | Semester | Prerequisites | Credits |

|-------|----------------|----------|---------------|---------|

| UG    | AEC533         | VI       | Embedded C    | 3       |

#### III. MARKS DISTRIBUTION:

| Subject                | SEE Examination | CIA Examination | Total<br>Marks |

|------------------------|-----------------|-----------------|----------------|

| Embedded System Design | 70 Marks        | 30 Marks        | 100            |

#### IV. DELIVERY / INSTRUCTIONAL METHODOLOGIES:

| ~ | LCD / PPT              | ~ | Seminars | > | Videos | > | MOOCs |

|---|------------------------|---|----------|---|--------|---|-------|

| × | Open Ended Experiments |   |          |   |        |   |       |

#### V. EVALUATION METHODOLOGY:

The course will be evaluated for a total of 100 marks, with 30 marks for Continuous Internal Assessment (CIA) and 70 marks for Semester End Examination (SEE). Out of 30 marks allotted for CIA during the semester, marks are awarded by taking average of two CIA examinations.

**Semester End Examination (SEE):** The SEE is conducted for 70 marks of 3 hours duration. The syllabus for the theory courses is divided into five units and each unit carries equal weightage in terms of marks distribution. The question paper pattern is as follows. Two full questions with "either" or "choice" will be drawn from each unit. Each question carries 14 marks. There could be a maximum of two sub divisions in a question.

The emphasis on the questions is broadly based on the following criteria:

|                                                    | 50 % | To test the objectiveness of the concept.    |  |

|----------------------------------------------------|------|----------------------------------------------|--|

|                                                    | 30 % | To test the analytical skill of the concept. |  |

| 20 % To test the application skill of the concept. |      |                                              |  |

#### **Continuous Internal Assessment (CIA):**

CIA is conducted for a total of 30 marks (Table 1), with 25 marks for Continuous Internal Examination (CIE), 05 marks for Technical Seminar and Term Paper.

| Table 1: Assessment pattern | for CIA |

|-----------------------------|---------|

|-----------------------------|---------|

| Component          | Tł       | leory                               | Total Marks |

|--------------------|----------|-------------------------------------|-------------|

| Type of Assessment | CIE Exam | Technical Seminar and<br>Term Paper |             |

| CIA Marks          | 25       | 05                                  | 30          |

#### **Continuous Internal Examination (CIE):**

Two CIE exams shall be conducted at the end of the 9<sup>th</sup> and 17<sup>th</sup> week of the semester respectively. The CIE exam is conducted for 25 marks of 2 hours duration, consisting of 5 one mark compulsory questions in part-A and 4 questions in part-B. The student has to answer any 4 questions out of five questions, each carries 5 marks. Marks are awarded by taking average of marks scored in two CIE exams.

#### **Technical Seminar and Term Paper:**

Two seminar presentations and the term paper with overview of topic are conducted during II semester. The evaluation of technical seminar and term paper is for maximum of 5 marks. Marks are awarded by taking average of marks scored in two Seminar Evaluations.

#### VI. HOW PROGRAM OUTCOMES ARE ASSESSED:

|      | Program Outcomes (POs)                                                                                                                                             | Strength | Proficiency assessed by                |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------|

| PO 1 | Apply advanced level knowledge, techniques, skills and                                                                                                             | 3        | Term paper                             |

|      | modern tools in the field of embedded system and sub                                                                                                               |          |                                        |

|      | areas IoT, Processor technology, storage technology.                                                                                                               |          |                                        |

| PO 2 | Function on multidisciplinary environments by working cooperatively, creatively and responsibly as a member                                                        | 2        | Term paper<br>and Guest Lectures       |

|      | of a team.                                                                                                                                                         |          |                                        |

| PO 3 | Respond to global policy initiatives and meet the<br>emerging challenges with sustainable technological<br>solutions in the field of electronic product designing. | 3        | Seminar and<br>Guest Lectures          |

| PO 4 | Demonstrate the importance of embedded technologies<br>and design new innovative products for solving society<br>relevant problems.                                | 3        | NPTEL Videos<br>and<br>Guest Lecturers |

#### **3** = **High; 2** = **Medium; 1** = Low

#### VII. COURSE OBJECTIVES:

#### The course should enable the students to:

| Ι   | To introduce the difference between embedded systems and general purpose systems. |

|-----|-----------------------------------------------------------------------------------|

| II  | To optimize hardware designs of custom single-purpose processors.                 |

| III | To compare different approaches in optimizing general-purpose processors.         |

| IV  | To introduce different peripheral interfaces to embedded systems.                 |

| V   | To understand the design tradeoffs made by different models of embedded systems.  |

| VI  | To apply knowledge gained in software-hardware integration in team-based projects |

#### VIII. COURSE OUTCOMES (COs):

| COs  | Course Outcome                            | CLOs  | Course Learning Outcome                                                    |

|------|-------------------------------------------|-------|----------------------------------------------------------------------------|

| CO 1 | Understand the basic concepts of Embedded | CLO 1 | Understand the definition of Embedded system and classification.           |

|      | systems and its applications.             | CLO 2 | Analyze the history of Embedded Systems and its applications.              |

|      |                                           | CLO 3 | Understand the characteristics and Quality Attributes of Embedded Systems. |

| COs  | Course Outcome                                                    | CLOs                                              | Course Learning Outcome                                                              |  |  |  |  |

|------|-------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

| CO 2 | Understand and analyze different processors in                    | CLO 4                                             | Describe general purpose and domain specific processors.                             |  |  |  |  |

|      | Embedded Systems                                                  | CLO 5                                             | Explain the concept of memory shadowing and memory selection for embedded systems.   |  |  |  |  |

|      |                                                                   | CLO 6                                             | Distinguish between onboard and external communication interfaces.                   |  |  |  |  |

| CO 3 | Describe about Embedded<br>Firmware design approaches             | CLO 7                                             | Watchdog Timer.                                                                      |  |  |  |  |

|      | and development languages.                                        | approaches.                                       |                                                                                      |  |  |  |  |

|      |                                                                   | CLO 9                                             | Describe the importance of Embedded Firmware development Languages.                  |  |  |  |  |

| CO 4 | Explain about Operating<br>System basics,                         | CLO 10                                            | Understand the importance of operating system basics and types of operating systems. |  |  |  |  |

|      | Multiprocessing and Multitasking.                                 | rocessing and CLO 11 Distinguish between Multipro |                                                                                      |  |  |  |  |

|      |                                                                   | CLO 12                                            | Explain about the concept of task scheduling.                                        |  |  |  |  |

| CO 5 | Describe about                                                    | CLO 13                                            | Describe about different Synchronization Issues.                                     |  |  |  |  |

|      | synchronization issues and<br>task synchronization<br>techniques. | CLO 14                                            | Analyze different task synchronization techniques.                                   |  |  |  |  |

|      | contractor.                                                       | CLO 15                                            | Understand the concept of how to choose an RTOS.                                     |  |  |  |  |

#### IX. COURSE LEARNING OUTCOMES(CLOs):

| CLO Code  | CLO's  | At the end of the course, the student will<br>have the ability to                    | PO's<br>Mapped | Strength<br>of Mapping |

|-----------|--------|--------------------------------------------------------------------------------------|----------------|------------------------|

| BESB01.01 | CLO 1  | Understand the definition of Embedded system and classification.                     | PO 1           | 2                      |

| BESB01.02 | CLO 2  | Analyze the history of Embedded Systems and its applications.                        | PO 1           | 2                      |

| BESB01.03 | CLO 3  | Understand the characteristics and Quality Attributes of Embedded Systems.           | PO 1, PO 3     | 1                      |

| BESB01.04 | CLO 4  | Describe general purpose and domain specific processors.                             | PO 2, PO 3     | 3                      |

| BESB01.05 | CLO 5  | Explain the concept of memory shadowing and memory selection for embedded systems.   | PO 1           | 3                      |

| BESB01.06 | CLO 6  | Distinguish between onboard and external communication interfaces.                   | PO 2           | 3                      |

| BESB01.07 | CLO 7  | Describe importance of Real Time Clock and Watchdog Timer.                           | PO 3           | 3                      |

| BESB01.08 | CLO 8  | Explain about Embedded firmware design approaches.                                   | PO 1, PO 3     | 2                      |

| BESB01.09 | CLO 9  | Describe the importance of Embedded Firmware development Languages.                  | PO 3, PO 4     | 2                      |

| BESB01.10 | CLO10  | Understand the importance of operating system basics and types of operating systems. | PO 1, PO 4     | 3                      |

| BESB01.11 | CLO 11 | Distinguish between Multiprocessing and Multitasking.                                | PO 3           | 2                      |

| BESB01.12                                                        | CLO 12 | Explain about the concept of task scheduling.      | PO3, PO 4  | 3 |  |  |  |

|------------------------------------------------------------------|--------|----------------------------------------------------|------------|---|--|--|--|

| BESB01.13                                                        | CLO 13 | Describe about different Synchronization Issues.   | PO 2       | 2 |  |  |  |

| BESB01.14                                                        | CLO 14 | Analyze different task synchronization techniques. | PO 3, PO 4 | 3 |  |  |  |

| BESB01.15                                                        | CLO 15 | Understand the concept of how to choose an RTOS.   | PO 3, PO 4 | 2 |  |  |  |

| $2 - \text{High} \cdot 2 - \text{Modium} \cdot 1 - \text{Low}^2$ |        |                                                    |            |   |  |  |  |

#### **3** = High; **2** = Medium; **1** = Low**2**

## X. MAPPING COURSE OUTCOMES LEADING TO THE ACHIEVEMENT OF PROGRAM OUTCOMES:

| Course Outcomes |      | Program Outcomes(PO) |      |      |  |  |

|-----------------|------|----------------------|------|------|--|--|

| (COs)           | PO 1 | PO 2                 | PO 3 | PO 4 |  |  |

| CO 1            | 3    |                      | 2    |      |  |  |

| CO 2            | 3    | 2                    | 2    |      |  |  |

| CO 3            | 2    |                      | 3    | 2    |  |  |

| CO 4            | 2    | 2                    | 2    | 2    |  |  |

| CO 5            |      | 2                    | 2    | 2    |  |  |

3 = High; 2 = Medium; 1 = Low2

## XI. MAPPING COURSE LEARNING OUTCOMES LEADING TO THE ACHIEVEMENT OF PROGRAM OUTCOMES:

| Course Learning    |      | Progra | m Outcome(PO) |      |

|--------------------|------|--------|---------------|------|

| Outcomes<br>(CLOs) | PO 1 | PO 2   | PO 3          | PO 4 |

| CLO 1              | 3    |        |               |      |

| CLO 2              | 3    |        |               |      |

| CLO 3              | 3    |        | 3             |      |

| CLO 4              |      | 3      | 2             |      |

| CLO 5              | 2    |        |               |      |

| CLO 6              |      | 2      |               |      |

| CLO 7              |      |        | 3             |      |

| CLO 8              | 2    |        | 3             |      |

| CLO 9              |      |        | 3             | 3    |

| CLO 10             | 3    |        |               | 3    |

| CLO 11 |   | 2 |   |

|--------|---|---|---|

| CLO 12 |   | 2 | 3 |

| CLO 13 | 2 |   |   |

| CLO 14 |   | 2 | 3 |

| CLO 15 |   | 2 | 2 |

**3** = High; **2** = Medium; **1** = Low

#### XII. ASSESSMENT METHODOLOGIES –DIRECT:

| CIE Exams | PO1, PO2, PO3,<br>PO 4 | SEE Exams    | PO1, PO2, PO3,<br>PO 4 | Seminar and<br>Term Paper | PO1, PO2, PO3, PO4 |

|-----------|------------------------|--------------|------------------------|---------------------------|--------------------|

| Viva      | -                      | Mini Project | -                      | Laboratory<br>Practices   | -                  |

#### XIII. ASSESSMENT METHODOLOGIES -- INDIRECT:

| ~ | Early Semester Feedback                | ~ | End Semester OBE Feedback |

|---|----------------------------------------|---|---------------------------|

| × | Assessment of Mini Projects by Experts |   |                           |

#### XIV. SYLLABUS:

| I Semester: ESD   PCC : CSE / SE / AE /(CAD /CAM) / PE/ST                              |                       |   |                        |   |   |                   |     |       |

|----------------------------------------------------------------------------------------|-----------------------|---|------------------------|---|---|-------------------|-----|-------|

| Course code         Category         Hours / Week         Credits         Maximum Mark |                       |   |                        |   |   | m Marks           |     |       |

| BES001                                                                                 | Core/Elective         | L | Т                      | Р | С | CIA               | SEE | Total |

| DESUUI                                                                                 |                       | 3 | -                      | - | 3 | 30                | 70  | 100   |

| Contact Classes: 45                                                                    | Tutorial Classes: Nil |   | Practical Classes: Nil |   |   | Total Classes: 45 |     |       |

#### **OBJECTIVES:**

The course should enable the students to:

- I. To introduce the difference between embedded systems and general purpose systems.

- II. To optimize hardware designs of custom single-purpose processors.

- III. To compare different approaches in optimizing general-purpose processors.

- IV. To introduce different peripheral interfaces to embedded systems.

- V. To understand the design tradeoffs made by different models of embedded systems.

- VI. To apply knowledge gained in software-hardware integration in team-based projects.

| Definition of Embedded System, Embedded Systems Vs General Computing Systems, History of Embedded          |              |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|

| Systems, Classification, Major Application Areas, Purpose of Embedded Systems, Characteristics and Quality |              |  |  |  |  |  |

| Attributes of Embedded Systems.                                                                            |              |  |  |  |  |  |

| UNIT-II TYPICAL EMBEDDED SYSTEM:                                                                           | Classes: 09  |  |  |  |  |  |

| Core of the Embedded System: General Purpose and Domain Specific Processors, ASICs, PLDs, Com              | mercial Off- |  |  |  |  |  |

| The-Shelf Components (COTS), Memory: ROM, RAM, Memory according to the type of Interfac                    | ice, Memory  |  |  |  |  |  |

| Shadowing, Memory selection for Embedded Systems, Sensors and Actuators, Communication Interfac            | ace: Onboard |  |  |  |  |  |

| and External Communication Interfaces.                                                                     |              |  |  |  |  |  |

|                                                                                                            |              |  |  |  |  |  |

| UNIT-III EMBEDDED FIRMWARE:                                                                                | Classes: 09  |  |  |  |  |  |

| Reset Circuit, Brown-out Protection Circuit, Oscillator Unit, Real Time Clock, Watchdog Timer,             | , Embedded   |  |  |  |  |  |

| Firmware Design Approaches and Development Languages.                                                      |              |  |  |  |  |  |

| RTOS BASED EMBEDDED SYSTEM DESIGN:                                                                         |              |  |  |  |  |  |

|                                                                                                            | Classes: 09  |  |  |  |  |  |

| Operating System Basics, Types of Operating Systems, Tasks, Process and Threads, Multiproc                 | ocessing and |  |  |  |  |  |

| Multitasking, Task Scheduling.                                                                             |              |  |  |  |  |  |

| UNIT-V TASK COMMUNICATION:                                                                                 | Classes: 09  |  |  |  |  |  |

| Shared Memory, Message Passing, Remote Procedure Call and Sockets, Task Synchronization: Task              |              |  |  |  |  |  |

| Communication/Synchronization Issues, Task Synchronization Techniques, Device Drivers, How to Choose an    |              |  |  |  |  |  |

| Communication/Synchronization Issues, Task Synchronization Techniques, Device Drivers, How to              | o Choose an  |  |  |  |  |  |

Classes: 09

#### **Text Books:**

UNIT-I

1. Embedded System Design - Frank Vahid, Tony Givargis, John Wiley.

INTRODUCTION TO EMBEDDED SYSTEMS:

#### **Reference Books:**

1. Embedded Systems - Raj Kamal, TMH.

2. Introduction to Embedded Systems - Shibu K.V, McGraw Hill.

3. Embedded Systems - Lyla, Pearson, 2013

4. An Embedded Software Primer - David E. Simon, Pearson Education.

#### **XV. COURSE PLAN:**

The course plan is meant as a guideline. There may probably be changes.

| Lecture | Topic Outcomes                                                      | Topic/s to be covered                          | Reference             |  |  |

|---------|---------------------------------------------------------------------|------------------------------------------------|-----------------------|--|--|

| No      | •                                                                   | •                                              |                       |  |  |

| 1-3     | Understand the definition of                                        | Definition of embedded system, embedded        | T1: 5.1, 5.2, R1: 1.7 |  |  |

|         | Embedded system and                                                 | systems vs general computing systems.          |                       |  |  |

|         | classification.                                                     |                                                |                       |  |  |

| 4-6     | Analyze the history of History of embedded systems, classification, |                                                | T1:6.1,6.2, 6.3, T1:  |  |  |

|         | Embedded Systems and its                                            | major application areas.                       | 6.4-6.6               |  |  |

|         | applications.                                                       |                                                |                       |  |  |

| 7-9     | Understand the characteristics                                      | e characteristics Purpose of embedded systems, |                       |  |  |

|         |                                                                     | characteristics and quality attributes of      | 6.15 R2:7.1, 8.1      |  |  |

| Lecture<br>No | Topic Outcomes                    | Topic/s to be covered                                     | Reference                |

|---------------|-----------------------------------|-----------------------------------------------------------|--------------------------|

|               | and Quality Attributes of         | embedded systems.                                         |                          |

|               | Embedded Systems.                 |                                                           |                          |

| 10-12         | Describe general purpose and      | Core of the embedded system: general                      | T1:7.1, 7.4 T1:7.7, 7.8- |

| 10 12         | domain specific processors.       | purpose and domain specific processors.                   | 7.10 R2:7.2              |

| 13-16         | Explain the concept of memory     | Basics, PLDs, commercial off-the-shelf                    | T1: 6.12, 9.4,9.6, R2:   |

| 15-10         |                                   | components (cots), memory: ROM, RAM,                      | 4.2,                     |

|               | shadowing and memory              | memory according to the type of interface,                | 1.2,                     |

|               | selection for embedded            | memory shadowing, memory selection for                    |                          |

|               | systems.                          | embedded systems.                                         |                          |

| 17-19         | Distinguish between onboard       | Sensors and actuators, communication                      | T1: 7.12,10.4, R2: 4.2,  |

|               | and external communication        | interface: onboard and external                           | T1: 10.6                 |

|               | interfaces.                       | communication interfaces.                                 |                          |

| 20-21         | Describe importance of Real       | Reset circuit, brown-out protection circuit,              | T1: 10.5, T1:            |

|               | Time Clock and Watchdog           | oscillator unit, real time clock, watchdog                | 8.1,8.2, 8.4,8.5,8.6     |

|               | Timer.                            | timer,                                                    | R2: 4.4                  |

| 22-25         | Explain about Embedded            | Embedded firmware design approaches.                      | T1: 8.2,8.9              |

|               | firmware design approaches.       |                                                           | R2: 4.4,                 |

| 26-30         | Describe the importance of        | Embedded firmware development                             | T1: 8.12, 8.13, 8.14     |

|               | Embedded Firmware                 | languages.                                                |                          |

|               | development Languages.            |                                                           |                          |

| 31-33         | Understand the importance of      | Operating system basics, types of operating               | T1: 9.1, 9.2,9.3         |

|               | operating system basics and       | systems.                                                  |                          |

|               | types of operating systems.       |                                                           |                          |

| 34-36         | Distinguish between               | Tasks, process and threads, multiprocessing               | R1:7.1,7.3 R1:7.4,7.7    |

|               | Multiprocessing and Multitasking. | and multitasking.                                         |                          |

| 37-39         | Explain about the concept of task | Task scheduling.                                          | T1: 8.12, 8.13, 8.14     |

|               | scheduling.                       |                                                           |                          |

| 40-41         | Describe about different          | Shared memory, message passing, remote                    | T1: 9.1, 9.2,9.3         |

|               | Synchronization Issues.           | procedure call and sockets, task<br>synchronization: task |                          |

|               |                                   | communication/synchronization issues.                     |                          |

| 42-44         | Analyze different task            | Task synchronization techniques                           | R1:7.1,7.3 R1:7.4,7.7    |

|               | synchronization techniques.       |                                                           |                          |

| 45            | Understand the concept of how to  | Device drivers, how to choose an RTOS.                    | T1: 9.1, 9.2,9.3         |

|               | choose an RTOS.                   |                                                           |                          |

#### XVI. GAPS IN THE SYLLABUS-TO MEET INDUSTRY /PROFESSIONAL REQUIREMENTS:

| S No | Description       | Proposed Actions                  | Relevance with POs  |

|------|-------------------|-----------------------------------|---------------------|

| 1    | Concepts of ERTOS | Seminars / Guest Lectures / NPTEL | PO 1, PO 2,<br>PO 4 |

**Prepared By:**

Mr. K Ravi, Assistant Professor

HOD, ECE

**INSTITUTE OF AERONAUTICAL ENGINEERING**

(Autonomous) Dundigal, Hyderabad -500 043

#### ELECTRONICS ANDCOMMUNICATION ENGINEERING

#### **COURSE DESCRIPTOR**

| Course Title      |                                               | MICROCONTROLLERS AND PROGRAMMABLE DIGITAL SIGNAL PROCESSING |           |         |            |         |

|-------------------|-----------------------------------------------|-------------------------------------------------------------|-----------|---------|------------|---------|

| Course Code       | BESB02                                        | BESB02                                                      |           |         |            |         |

| Programme         | M.Tech                                        | (ES                                                         | )         |         |            |         |

| Semester          | Ι                                             | ECE                                                         | 2         |         |            |         |

| Course Type       | Core                                          |                                                             |           |         |            |         |

| Regulation        | IARE - R                                      | 18                                                          |           |         |            |         |

|                   | Theory Practical                              |                                                             |           |         |            | cal     |

| Course Structure  | Lectur                                        | res                                                         | Tutorials | Credits | Laboratory | Credits |

|                   | 3                                             |                                                             | -         | 3       | -          | -       |

| Chief Coordinator | Dr. P Munaswami, Professor, ECE               |                                                             |           |         |            |         |

| Course Faculty    | Mr. V. Naresh Kumar, Assistant Professor, ECE |                                                             |           |         |            |         |

#### I. COURSE OVERVIEW:

This course starts by introducing some basic ideas of ARM Cortex-M3 Processor and LPC 17XX Microcontroller architectures and their features. Subsequently the course covers Programmable DSP Processor architecture. As we progress with the course students will be familiarized with the programming models of Microcontrollers and P-DSPs and their applications in real world.

#### II. COURSE PRE-REQUISITES:

| Level | <b>Course Code</b> | Semester | Prerequisites          | Credits |

|-------|--------------------|----------|------------------------|---------|

| PG    | BESB01             | Ι        | Embedded System Design | 3       |

#### **III. MARKS DISTRIBUTION:**

| Subject                                                        | SEE Examination | CIA Examination | Total Marks |

|----------------------------------------------------------------|-----------------|-----------------|-------------|

| Microcontrollers And Programmable<br>Digital Signal Processing | 70 Marks        | 30 Marks        | 100         |

#### IV. DELIVERY / INSTRUCTIONAL METHODOLOGIES:

| ~ | Chalk & Talk             | ~ | Quiz     | ~ | Assignments  | × | MOOCs  |  |

|---|--------------------------|---|----------|---|--------------|---|--------|--|

| ~ | LCD / PPT                | ~ | Seminars | ~ | Mini Project | × | Videos |  |

| × | ✗ Open Ended Experiments |   |          |   |              |   |        |  |

#### V. EVALUATION METHODOLOGY:

The course will be evaluated for a total of 100 marks, with 30 marks for Continuous Internal Assessment (CIA) and 70 marks for Semester End Examination (SEE). Out of 30 marks allotted for CIA during the semester, marks are awarded by taking average of two CIA examinations or the marks scored in the make- examination.

**Semester End Examination (SEE):** The SEE shall be conducted for 70 marks of 3 hours duration. The syllabus for the theory courses shall be divided into FIVE units and each unit carries equal weight age in terms of marks distribution. The question paper pattern shall be as defined below. Two full questions with 'either' 'or' choice will be drawn from each unit. Each question carries 14 marks. There could be a maximum of three sub divisions in a question.

The emphasis on the questions is broadly based on the following criteria:

| 50 % | To test the objectiveness of the concept.     |  |  |  |

|------|-----------------------------------------------|--|--|--|

| 30 % | To test the analytical skill of the concept.  |  |  |  |

| 20 % | To test the application skill of the concept. |  |  |  |

#### **Continuous Internal Assessment (CIA):**

CIA is conducted for a total of 30 marks (Table 1), with 25 marks for Continuous Internal Examination (CIE), 05 marks for Technical Seminar and Term Paper.

| Component          |          | T-4-1 Marsler                       |             |

|--------------------|----------|-------------------------------------|-------------|

| Type of Assessment | CIE Exam | Technical Seminar and Term<br>Paper | Total Marks |

| CIA Marks          | 25       | 5                                   | 30          |

#### **Continuous Internal Examination (CIE):**

Two CIE exams shall be conducted at the end of the 9th and 17th week of the semester respectively. The CIE exam is conducted for 25 marks of 2 hours duration, consisting of 5 one mark compulsory questions in part-A and 4 questions in part-B. The student has to answer any 4 questions out of five questions, each carrying 5 marks. Marks are awarded by taking average of marks scored in two CIE exams.

#### **Technical Seminar and Term Paper:**

Two seminar presentations are conducted during I year I semester and II semester. For seminar, a student under the supervision of a concerned faculty member, shall identify a topic in each course and prepare the term paper with overview of topic. The evaluation of Technical seminar and term paper is for maximum of 5 marks. Marks are awarded by taking average of marks scored in two Seminar Evaluations.

#### VI. HOW PROGRAM OUTCOMES ARE ASSESSED:

|      | Program Outcomes (POs)                                      | Strength | Proficiency<br>assessed by |

|------|-------------------------------------------------------------|----------|----------------------------|

| PO 1 | Independently carry out research/investigation and          | 2        | Quiz                       |

|      | development work to solve practical problems                |          |                            |

| PO 3 | Apply advanced level knowledge, techniques, skills and      | 2        | Assignments                |

|      | modern tools in the field of Embedded Systems.              |          |                            |

| PO 6 | Understand the importance of embedded technologies and      | 3        | Seminars                   |

|      | design new innovative products for solving society relevant |          |                            |

|      | problems                                                    |          |                            |

| PO 7 | Recognize the need to engage in lifelong learning through   | 2        | Term paper                 |

|      | continuing education and research.                          |          |                            |

**3= High; 2 = Medium; 1 = Low**

#### VII COURSE OBJECTIVES:

#### The course should enable the students to:

| Ι   | Compare and select ARM processor core based SoC with several features/peripherals based on requirements of embedded applications. |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|

| II  | Identify and characterize architecture of Programmable DSP Processors                                                             |

| III | Develop small applications by utilizing the ARM processor core and DSP processor based platform                                   |

#### VIII COURSE OUTCOMES (COs):

| COs  | Course Outcome                                      | CLOs   | Course Learning Outcome                                                                                                                                      |

|------|-----------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CO 1 | Describe different<br>ARM processors,               | CLO 1  | Understanding the ARM Cortex-M3 processor:<br>Applications, Programming model – Registers,<br>Operation modes, Exceptions and Interrupts,<br>Reset Sequence. |

|      | programming models,<br>operations and<br>interrupts | CLO 2  | Study the Instruction Set, Unified Assembler<br>Language, Memory Maps, Memory Access<br>Attributes, Permissions, Bit-Band Operations.                        |

|      | interrupts.                                         | CLO 3  | Discuss the Unaligned and Exclusive Transfers.<br>Pipeline, Bus Interfaces.                                                                                  |

| CO 2 | Demonstrate various<br>exceptions, interrupts,      | CLO 4  | Examine the various Exceptions, Types, Priority,<br>Vector Tables, Interrupt Inputs and Pending<br>behavior, Fault Exceptions                                |

|      | configurations, interrupt latency.                  | CLO 5  | Discuss the Supervisor and Pendable Service<br>Call, Nested Vectored Interrupt Controller.                                                                   |

|      |                                                     | CLO 6  | Understand the Basic Configuration, SYSTICK<br>Timer, Interrupt Sequences, Exits, Tail Chaining,<br>Interrupt Latency.                                       |

| CO 3 | Describe the operation, feature of the LPC 17xx     | CLO 7  | Describe the LPC 17xx microcontroller- Internal memory, GPIOs, Timers.                                                                                       |

|      | microcontroller.                                    | CLO 8  | Study the features of ADC, UART and other serial interfaces.                                                                                                 |

|      |                                                     | CLO 9  | Understand the concepts of PWM, RTC, WDT.                                                                                                                    |

| CO 4 | Describe the programmable DSP                       | CLO 10 | Describe the Programmable DSP (P-DSP)<br>Processors: Harvard architecture, Multi port<br>memory.                                                             |

| COs  | Course Outcome                                       | CLOs   | Course Learning Outcome                                                                                                                                              |

|------|------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | processor and TI DSP processor.                      | CLO 11 | Study the features of architectural structure of P-<br>DSP- MAC unit, Barrel shifters.                                                                               |

|      | processor.                                           | CLO 12 | Understand the Introduction to TI DSP processor family.                                                                                                              |

| CO 5 | Design and development<br>architectural patterns and | CLO 13 | Study the VLIW architecture and TMS320C6000 series, architecture study, data paths, cross paths.                                                                     |

|      | reference models.                                    | CLO 14 | Understand the Introduction to Instruction level<br>architecture of C6000 family, Assembly<br>Instructions memory addressing, for arithmetic,<br>logical operations. |

|      |                                                      | CLO 15 | Describe the Code Composer Studio for<br>application development for digital signal<br>processing, On chip peripherals, Processor<br>benchmarking.                   |

#### IX. COURSE LEARNING OUTCOMES (CLOs):

| CLO       | CLO's  | At the end of the course, the student     | PO's   | Strength of |

|-----------|--------|-------------------------------------------|--------|-------------|

| Code      |        | will have the ability to:                 | Mapped | Mapping     |

| BESB02.01 | CLO 1  | Understanding the ARM Cortex-M3           | PO1    | 3           |

|           |        | processor: Applications, Programming      |        |             |

|           |        | model - Registers, Operation modes,       |        |             |

|           |        | Exceptions and Interrupts, Reset          |        |             |

|           |        | Sequence.                                 |        |             |

| BESB02.02 | CLO 2  | Study the Instruction Set, Unified        | PO1    | 2           |

|           |        | Assembler Language, Memory Maps,          |        |             |

|           |        | Memory Access Attributes, Permissions,    |        |             |

|           |        | Bit-Band Operations.                      |        |             |

| BESB02.03 | CLO 3  | Discuss the Unaligned and Exclusive       | PO3    | 2           |

|           |        | Transfers. Pipeline, Bus Interfaces.      |        |             |

| BESB02.04 | CLO 4  | Examine the various Exceptions, Types,    | PO1    | 2           |

|           |        | Priority, Vector Tables, Interrupt Inputs | PO6    |             |

|           |        | and Pending behavior, Fault Exceptions    |        |             |

| BESB02.05 | CLO 5  | Discuss the Supervisor and Pendable       | PO1    | 2           |

|           |        | Service Call, Nested Vectored Interrupt   | PO7    |             |

|           |        | Controller.                               |        |             |

| BESB02.06 | CLO 6  | Understand the Basic Configuration,       | PO3    | 3           |

|           |        | SYSTICK Timer, Interrupt Sequences,       |        |             |

|           |        | Exits, Tail Chaining, Interrupt Latency.  |        |             |

| BESB02.07 | CLO 7  | Describe the LPC 17xx microcontroller-    | PO7    | 3           |

|           |        | Internal memory, GPIOs, Timers.           |        |             |

| BESB02.08 | CLO 8  | Study the features of ADC, UART and       | PO1    | 2           |

|           |        | other serial interfaces.                  |        |             |

| BESB02.09 | CLO 9  | Understand the concepts of PWM, RTC,      | PO3    | 2           |

|           |        | WDT.                                      | PO6    |             |

| BESB02.10 | CLO 10 | Describe the Programmable DSP (P-DSP)     | PO1    | 2           |

|           |        | Processors: Harvard architecture, Multi   | PO7    |             |

|           |        | port memory.                              |        |             |

| BESB02.11 | CLO 11 | Study the features of architectural       | PO1    | 2           |

|           |        | structure of P-DSP- MAC unit, Barrel      |        |             |

|           |        | shifters.                                 |        |             |

| BESB02.12 | CLO 12 | Understand the Introduction to TI DSP     | PO6    | 2           |

|           |        | processor family.                         |        |             |

| BESB02.13 | CLO 13 | Study the VLIW architecture and           | PO1    | 2           |

|           |        | TMS320C6000 series, architecture study,   |        |             |

|           |        | data paths, cross paths.                  |        |             |

| CLO<br>Code | CLO's  | At the end of the course, the student<br>will have the ability to:                                                                                                      | PO's<br>Mapped | Strength of<br>Mapping |

|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------|

| BESB02.14   | CLO 14 | Understand the Introduction to Instruction<br>level architecture of C6000 family,<br>Assembly Instructions memory<br>addressing, for arithmetic, logical<br>operations. | PO3            | 3                      |

| BESB02.15   | CLO 15 | Describe the Code Composer Studio for<br>application development for digital signal<br>processing, On chip peripherals, Processor<br>benchmarking.                      | PO1            | 2                      |

**3= High; 2 = Medium; 1 = Low**

## X. MAPPING COURSE OUTCOMES LEADING TO THE ACHIEVEMENT OF PROGRAM OUTCOMES:

| Course            | Program Outcomes (PO) |      |             |      |  |  |  |

|-------------------|-----------------------|------|-------------|------|--|--|--|

| Outcomes<br>(COs) | PO 1                  | PO 3 | <b>PO 6</b> | PO 7 |  |  |  |

| CO 1              | 3                     | 2    |             |      |  |  |  |

| CO 2              | 2                     | 3    | 2           | 2    |  |  |  |

| CO 3              | 2                     | 2    | 2           | 3    |  |  |  |

| CO 4              | 2                     |      | 2           | 2    |  |  |  |

| CO 5              | 2                     | 3    |             |      |  |  |  |

**3= High; 2 = Medium; 1 = Low**

## XI. MAPPING COURSE LEARNING OUTCOMES LEADING TO THE ACHIEVEMENT OF PROGRAM OUTCOMES AND PROGRAM SPECIFIC OUTCOMES:

| CL O   | POs |     |     |     |  |  |

|--------|-----|-----|-----|-----|--|--|

| CLOs   | PO1 | PO3 | PO6 | PO7 |  |  |

| CLO 1  | 3   |     |     |     |  |  |

| CLO 2  | 2   |     |     |     |  |  |

| CLO 3  |     | 2   |     |     |  |  |

| CLO 4  | 2   |     | 2   |     |  |  |

| CLO 5  | 2   |     |     | 2   |  |  |

| CLO 6  |     | 3   |     |     |  |  |

| CLO 7  |     |     |     | 3   |  |  |

| CLO 8  | 2   |     |     |     |  |  |

| CLO 9  |     | 2   | 2   |     |  |  |

| CLO 10 | 2   |     |     | 2   |  |  |

| CLO 11 | 2   |     |     |     |  |  |

| CLO 12 |     |     | 2   |     |  |  |

| CLO 13 | 2   |     |     |     |  |  |

| CLO 14 |     | 3   |     |     |  |  |

| CLO 15 | 2   |     |     |     |  |  |

**3= High; 2 = Medium; 1 = Low**

#### XII. ASSESSMENT METHODOLOGIES-DIRECT:

| CIE Exams               | PO 1, PO 3<br>PO 6, PO 7 | SEE Exams       | PO 1, PO 3<br>PO 6, PO 7 | Assignments     | PO 3 | Seminars      | PO 6 |

|-------------------------|--------------------------|-----------------|--------------------------|-----------------|------|---------------|------|

| Laboratory<br>Practices | -                        | Student<br>Viva | -                        | Mini<br>Project | -    | Certification | -    |

| Term<br>Paper           | PO 6                     |                 |                          |                 |      |               |      |

#### XIII. ASSESSMENT METHODOLOGIES-INDIRECT:

| ~ | Early Semester Feedback                | ~ | End Semester OBE Feedback |

|---|----------------------------------------|---|---------------------------|

| × | Assessment of Mini Projects by Experts |   |                           |

#### **XIV. SYLLABUS:**